삼성전기, 첨단 패키징 '2.1D' 주목…"미래 HBM 시대 대세될 것"

[지디넷코리아]

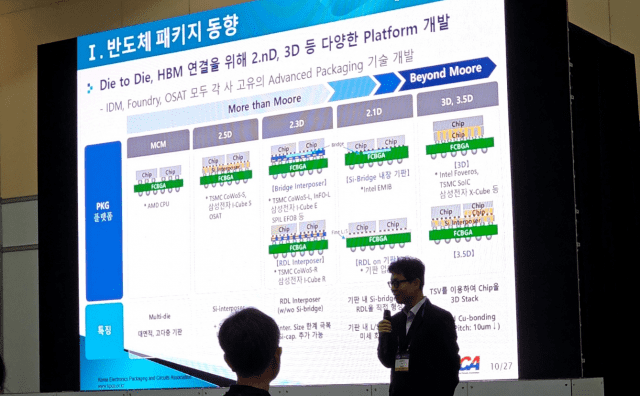

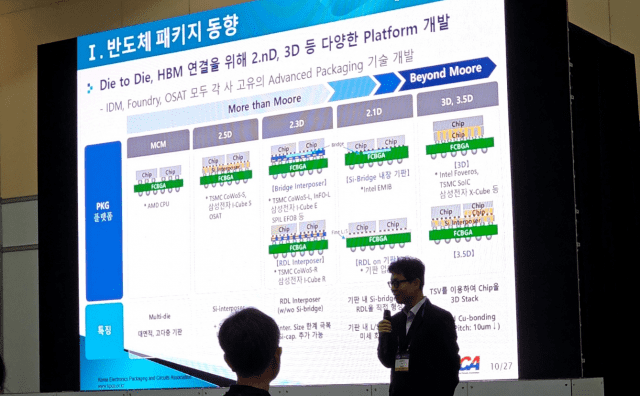

삼성전기가 최첨단 패키징 기술의 일종인 '2.1D' 시장에 주목하고 있다. 2.1D 패키징은 삼성전기와 같은 기판업체가 주도할 수 있는 기술로, 향후 HBM(고대역폭메모리)를 10개 이상 탑재하는 시장에서 본격 활용될 것으로 전망된다.

6일 김용훈 삼성전기 패키지마케팅 그룹장은 인천 송도 컨벤시아에서 열린 'KPCA show 2023(국제PCB 및 반도체패키징산업전)' 국제심포지엄에서 회사의 차세대 패키지기판 기술의 발전 전략에 대해 이같이 밝혔다.

반도체 패키지기판은 반도체 칩과 메인보드를 연결해 전기적 신호와 전력을 전달하는 부품이다. AI 등 첨단 산업의 발달로 반도체 성능이 급격히 높아지면서, 패키지기판도 이에 대응하기 위해 다층화, 대면적화 등으로 발전하고 있다.

특히 패키징 기술은 삼성전자, SK하이닉스 등이 미래 성장동력으로 삼고 있는 HBM과도 깊은 연관이 있다. HBM은 여러 개의 D램을 수직으로 적층해 기존 D램 대비 데이터 처리 속도를 높인 메모리다. 이 HBM을 로직반도체와 연결해 AI칩을 만들기 위해서는 2.5D 패키징과 같은 기술이 활용된다.

2.5D 패키징은 넓은 기판 모양의 실리콘 인터포저 위에 반도체 다이(Die)들을 수평 배치하는 기술이다. 대만 주요 파운드리인 TSMC가 엔비디아, AMD의 AI칩을 양산할 때 2.5D 패키징 기술을 활용하고 있다. 삼성전자 역시 관련 기술 고도화에 적극 나서는 중이다.

그러나 AI칩 내 HBM 탑재 수가 현재 6~8개에서 향후 10~12개로 증가하게 되면, 2.5D 패키징의 한계가 나타날 것이라는 게 김용훈 그룹장의 설명이다.

김용훈 그룹장은 "HBM 탑재 수가 10개 이상으로 넘어가면 인터포저 사이즈가 커질 수 밖에 없는데, 이렇게 되면 웨이퍼 한장 당 생산 가능한 제품 수가 줄어든다"며 "때문에 여러 업체가 비용 효율성을 높이기 위한 2.3D, 2.1D 등 대안 기술을 개발 중"이라고 밝혔다.

이 중 삼성전기는 2.1D 기술에 주목하고 있다. 2.5D나 2.3D(2.5D에서 실리콘 비아(Via)를 제거한 기술)는 패키징의 영향이 절대적이다. 반면 2.1D는 기판 기술에 큰 영향을 받기 때문에, 기판업체가 산업을 주도적으로 확장할 수 있는 시장이다.

2.1D는 실리콘 인터포저를 기판에 내장하는 '실리콘 브릿지'를 쓰거나, RDL이라 불리는 미세한 회로 패턴을 기판에 새기는 기술이다. 이를 활용하면 HBM 탑재 수 증가에 따른 생산 효율성 감소에 따른 문제를 해결할 수 있다.

김 그룹장은 "현재 엔비디아가 주도하고 있는 AI칩 시장의 메인은 HBM을 6개 탑재한 구조로, 2.5D 패키징이 안정화 돼 있다"며 "그러나 향후 HBM을 10~12개 탑재하는 경우에는 2.3D나 2.1D 기술이 대세화 될 것"이라고 말했다.

상용화 시점에 대해서는 "현재 TSMC가 다수의 고객사들과 2.3D, 2.1D 패키징을 통한 12 HBM 칩 양산을 테스트하고 있다"며 "3년 뒤까지 태동기를 거치고 나서, 그 이후부터 시장이 커질 수 있을 것"이라고 밝혔다.